### A Microcontroller for Everyone

Maker Faire May 21-22, 2011

Chen-Hanson Ting Silicon Valley Forth Interest Group

## Summary

- DIY microcontroller

- CPU hardware design in FPGA

- Operating system and programming language in Forth

- Demonstrations

## **DIY Microcontroller**

- Lattice XP2 Brevia Kit is a complete FPGA development system for \$49.

- The FPGA chip on Lattice Brevia Kit lets us design and implement your own microcontrollers.

- A 32-bit Forth microcontroller eP32 is demonstrated here.

## Microcontroller for Everyone

- For \$49, you can design, build and test your own microcontroller.

- The on-board FPGA chip, LatticeXP5E, can host a complete 32-bit microcontroller system.

- eP32 is implemented in VHDL, with Forth operating system and programming language.

## Microcontroller in FPGA

- Brevia Kit has all hardware components for a microcontroller system.

- LatticeXP2-5E 6TN144C FPGA chip has enough gates and RAM/ROM memory to host a complete 32-bit microcontroller.

- Lattice provides free hardware design tools.

- eForth provides an operating system and Forth programming language.

### LatticeXP2 Brevia Kit

## Free Hardware Design Tools

- Synthesis: Synplify

- Simulation: Active-HDL from Aldec

- Layout: Design Planner

- Flash Programming: ispVMR

- Tracing and Debugging: ispReveal

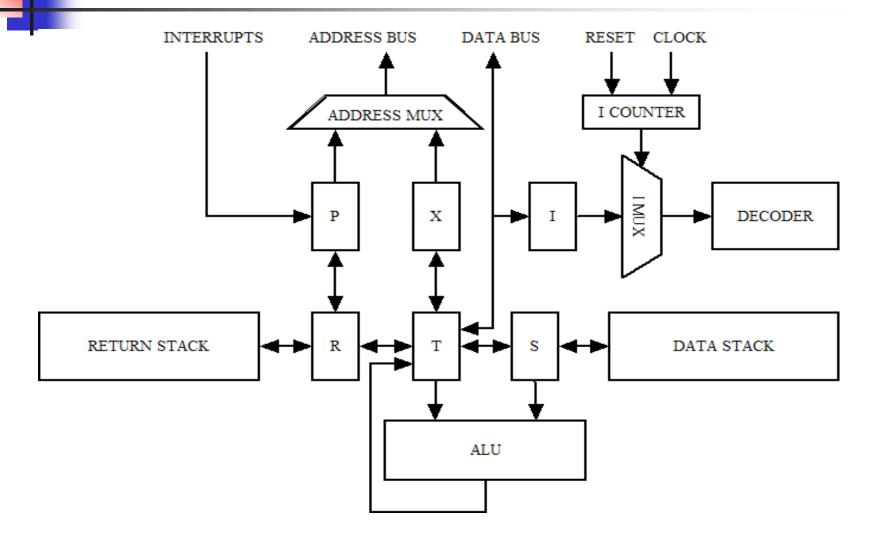

## Architecture of eP32 CPU

- A 32-bit CPU (Central Processing Unit)

- Two stacks to support Forth Language:

- Return stack for nested return addresses

- Parameter stack to pass parameters among nested subroutines

- Minimal instruction set

- Single clock cycle execution time

- Optimized subroutine call and return

### Block Diagram of eP32 CPU

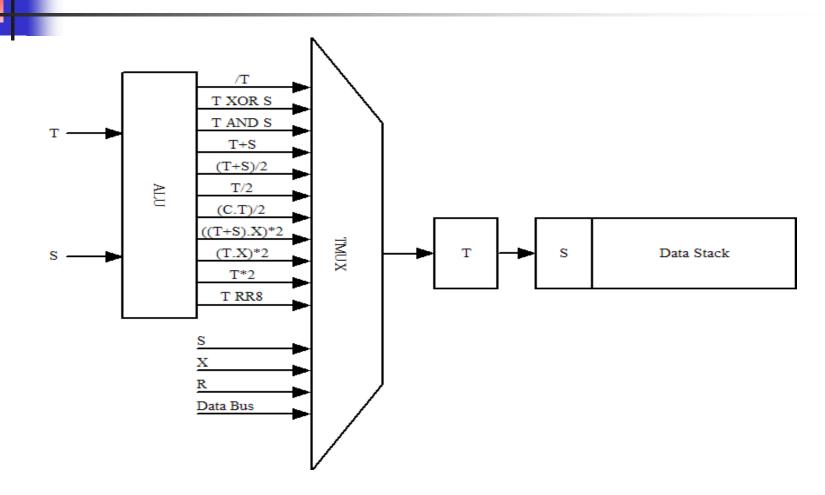

#### ALU and Data Processing Unit

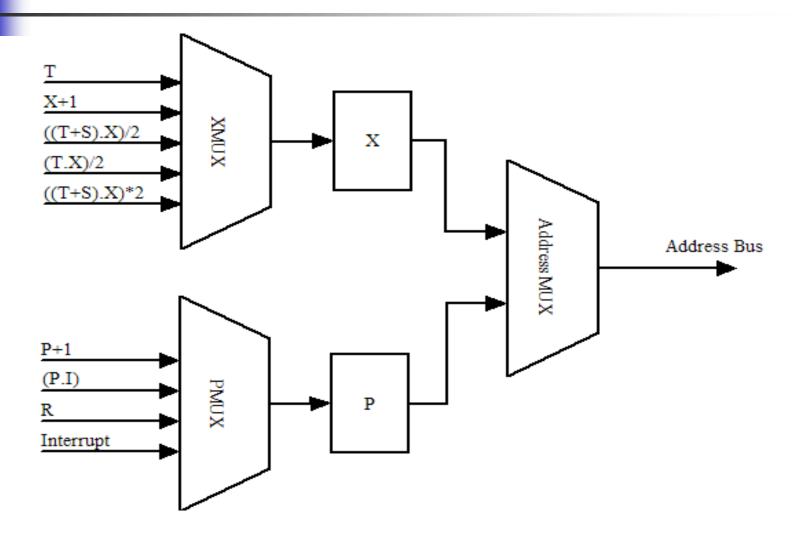

#### Program and Data Memory Unit

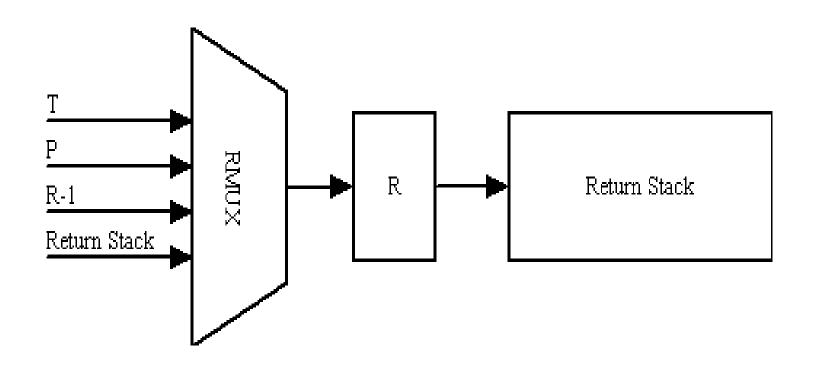

#### **Return Address Processing Unit**

#### **Instruction Execution Unit**

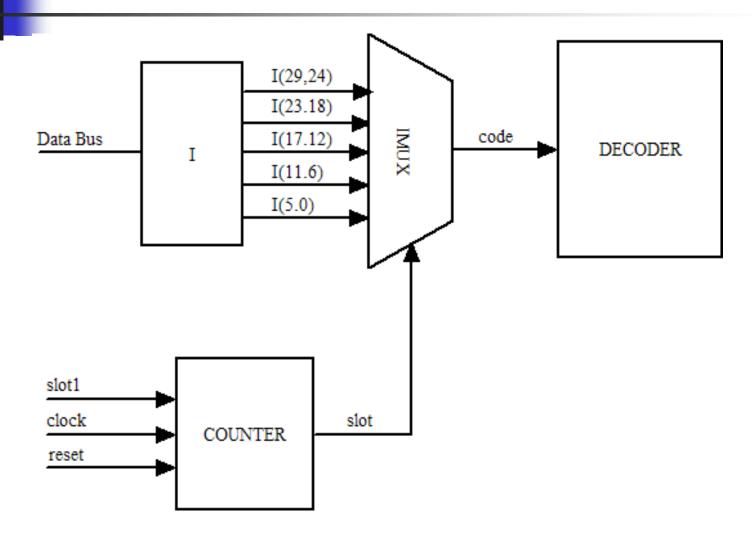

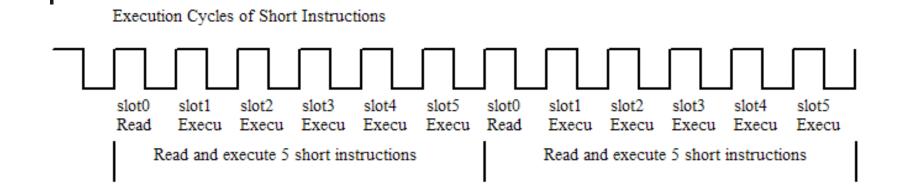

### **Instruction Execution Timing**

Execution Cycles of Long Instructions

### Instruction Set of eP32 CPU

- Minimum Instruction Set Computer (MISC)

- Only 27 Instructions, expandable to 64 instructions

- 4 Types of instructions:

- Program transfer instructions

- Memory access instructions

- ALU instructions

- Register and stack instructions

#### **Program Transfer Instructions**

- BRA Branch always

- RET Return from subroutine

- BZ Branch on zero

- BC Branch on carry

- CALL Call subroutine

- NEXT Loop until R is 0

#### Memory Access Instructions

- LDX Load from memory

- LDXP Load from memory and increment X register

- LDI Load immediate value

- STX Store to memory

- STXP Store to memory and increment X register

#### **ALU Instructions**

ADDAND

SHL

RR8

DIV

- Add S to T AND S to T

- XOR XOR S to T

- COM One's Complement of T

- SHR Shift T to right

- Shift T to left

- Rotate T right by 8 bits

- MUL Multiplication step

- **Division step**

#### **Register and Stack Instructions**

DUP Duplicate T to S DROP Pop S to T Push T to R PUSH POP Pop R to T OVER Duplicate S over T Load X to T TX Store T to X NOP No operation

### eP32 Microcontroller in VHDL

- eP32\_chip.vhd, top level design

- eP32q\_tb.vhd, test bench

- Modules

- eP32.vhd, CPU core

- Ram\_memory.vhd, 4096x32 autoinitialized RAM memory

- Uart.vhd, 115200 baud

- Gpio.vhd, 16 bit bidirectional

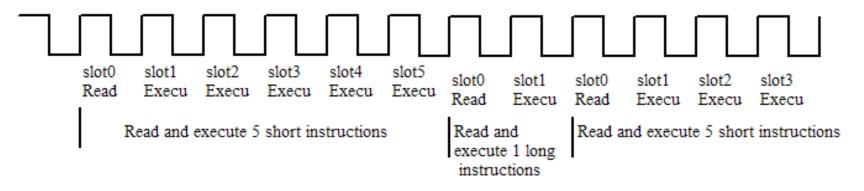

# Synthesizing eP32

- Ep32.vhd, uart.vhd and gpio.vhd are synthesized without modification

- Ram\_memory.vhd must be constructed to use RAM\_Q modules in LatticeXP2-5E FPGA chip.

- Ep32\_chip.vhd instantiates new ram\_memory.vhd with all other modules

# Simulating eP32

- Active-HDL simulation tools are supplied by Aldec.

- It needs a test bench module for functional simulation of eP32 chip: ep32q\_tb.vhd

| Active-HDL 8.2 (work ,w                          | vork) - D:\ispTool\Demo                                              | _LatticeXP2_Brevia_So                               | C_¥HDL\Demo_L           | atticeXP2_Brevia_SoC | Spr 🔳 🗖 🗙         |

|--------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------|-------------------------|----------------------|-------------------|

| <u>F</u> ile <u>E</u> dit Search <u>V</u> iew Wo | urkspace <u>D</u> esign <u>S</u> imulation                           | n <u>W</u> aveform <u>T</u> ools <u>W</u> i         | ndow <u>H</u> elp       |                      | ↔ ×               |

| 🗿 ▾ 🛩 🖬 🐹 📖 🖩                                    | I 🚯 💱 📃 🔎 🔛 I                                                        | 號 🍰 🔍 🎁 🚏 🖓                                         | 🗛 🐼 🕒 🤄                 | > 😂 🈓 📘 🕨 🖠          | 🕨 100 ns 🕂 📢 👋    |

| Design Brows ×                                   |                                                                      |                                                     |                         | ₩ AR 🔊 🖭 🛨           |                   |

| 🛐 testbench (behavior) 👻                         | Name VS 12                                                           |                                                     |                         |                      | 20 1 240 1 260 15 |

|                                                  | aclk 1                                                               |                                                     |                         |                      |                   |

| E-1 testbench (beha A<br>E-1 uut : ep32_chi      | nr aclk 1                                                            |                                                     |                         |                      |                   |

|                                                  | nor anst 1                                                           |                                                     |                         |                      |                   |

| bine                                             | + ar interrupt_i (UU                                                 |                                                     |                         |                      |                   |

| line                                             | + ™ ioport (2222                                                     |                                                     |                         |                      |                   |

| - Dine_<br>- Dine_                               | nr uart i 1                                                          |                                                     |                         |                      |                   |

|                                                  | nuart_o 1                                                            |                                                     |                         |                      |                   |

|                                                  |                                                                      | χ                                                   | 001 X000008D            | X0000068B X0000640   | χ0000641          |

|                                                  | 🛨 🖻 data_i 🦳                                                         | (000068D                                            | X0000000 X040           | 10640 X04000332 )    | (0A298798 X000    |

| Name                                             | <u></u> (IВ                                                          | χ                                                   |                         | <br>                 | <u></u>           |

| + " s_stack(4)                                   |                                                                      |                                                     |                         |                      |                   |

|                                                  |                                                                      |                                                     |                         |                      |                   |

| ± ‴ s_stack(2)                                   |                                                                      |                                                     |                         |                      |                   |

|                                                  |                                                                      |                                                     |                         |                      |                   |

| <b>∓</b> <sup>™</sup> s_stack(0)                 |                                                                      |                                                     |                         |                      |                   |

| 🛨 🏧 r_stack                                      |                                                                      |                                                     |                         |                      |                   |

| nr slot 💽                                        |                                                                      |                                                     |                         |                      | -                 |

|                                                  |                                                                      |                                                     |                         |                      | + 0 +             |

| ÈF/≌R/                                           | Eep32_chip)≡ e                                                       | ep32.vhd 👌 🗟 wavefo                                 | orm                     |                      |                   |

| • # KERNEL: Time: 0 ns. 1                        | -<br>Iteration: 2, Instance: /uut/cpu                                | 1. Process: line 133.                               |                         |                      |                   |

| × • # KERNEL: WARNING:                           | There is an UIXIWIZI-'in                                             | an arithmetic operand, the :                        | result will be 'X'(es). |                      |                   |

| 🔤 🔐 KEDNEL - WADNÍNG-                            | Iteration: 2, Instance: Auut, Pi<br>: There is an 'U'IX'IW'IZ'I-' in | rocess: line_197.<br>1 an arithmetic operand, the : | esult will be 'X'(es).  |                      |                   |

| 😚 🛛 - # KERNEL: Time: Ops, 1                     | Iteration: 2, Instance: Auut, Pi                                     | rocess: line_197.                                   |                         |                      | ~                 |

| • # KERNEL: Time: 0 ps, 1                        |                                                                      |                                                     |                         |                      |                   |

| 🔍 👤 Console /                                    |                                                                      |                                                     |                         |                      |                   |

|                                                  |                                                                      |                                                     |                         |                      |                   |

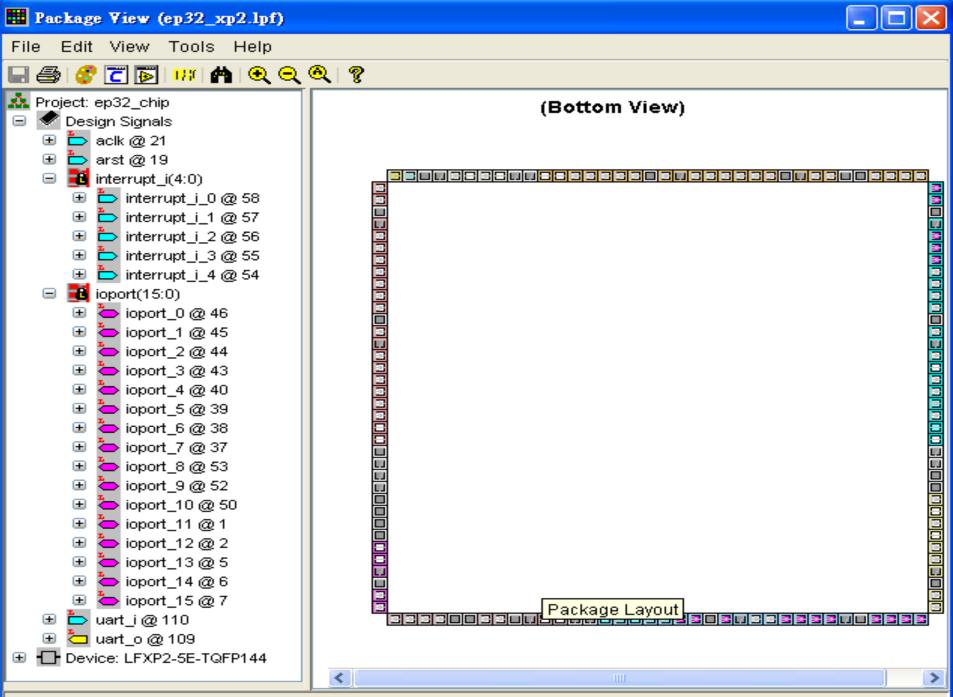

## Layout of eP32

Design Planner to assign following signals to physical pins:

- External reset

- External master clock

- Interrupts

- GPIO to LED and switches

- UART transmit

- UART receiver

Site 60:VCCAUX; Bank 99: 0 assigned/27 total

# Programming XP25E FPGA

- Connect JTAG cable to printer port.

- Connect UART cable to COM port.

- Invoke ispVMR system to download ep32\_xp2.jed file.

- eP32 eForth boots up and sends signon message to Hyperterminal console.

## Software Development Tools

- A metacompiler written in Forth includes:

- eP32 machine code assembler

- A nucleus of eP32 commands

- Text interpreter

- Compiler for new command

- Debugging tools

- eP32 software Simulator

### eForth System for eP32

- eForth is a complete Forth operating system produced by the metacompiler.

- Binary memory image is produced to be synthesized with eP32 CPU.

- Application software can be written, tested, and debugged under eForth.

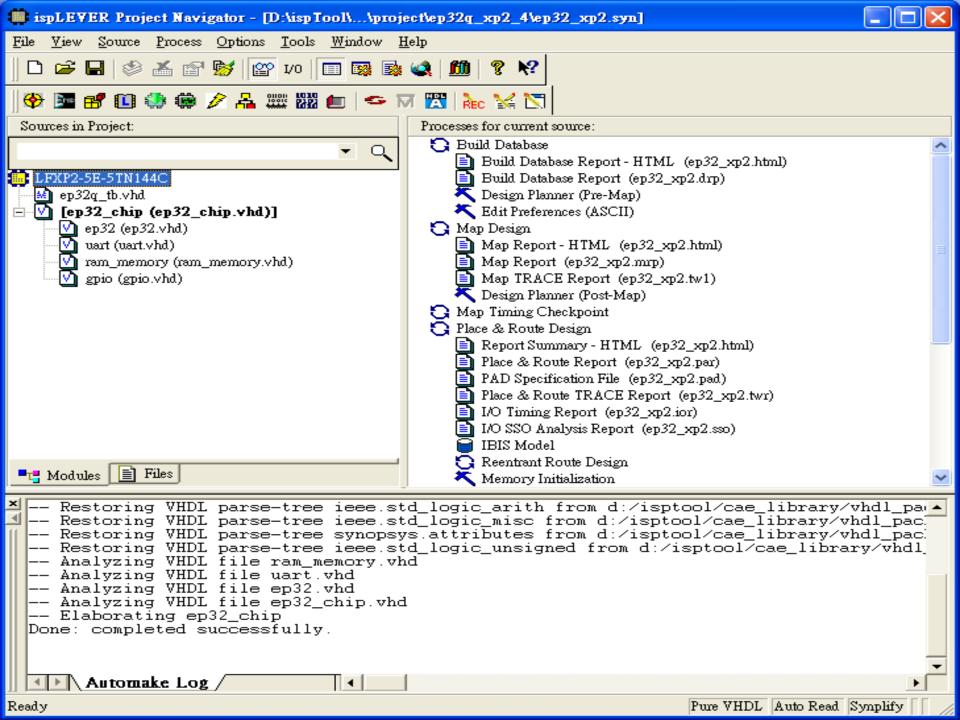

### Demonstration

- Boot up eForth on eP32

- Universal greeting "Hello, World!"

- Turn LED's on and off

- Read switches and push buttoms

#### Demonstrations

| 檔案 E 編輯 E 檢視 Y 呼叫 C 轉送 T 說明 E<br>○ K<br>OK<br>OK<br>OK<br>OK<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OK<br>OK<br>OK<br>eP32q v2.05<br>: TEST1 CR ." HELLO, WORLD!" ; OK<br>OK<br>TEST1<br>HELLO, WORLD! OK<br>OK<br>HEX OK<br>FF E00000001 ! OK<br>OK<br>CK<br>FE E00000000 ! OK<br>OK<br>E0000000 ! OK |

| <pre>eP32q v2.05<br/>: TEST1 CR ." HELLO, WORLD!" ; 0K</pre>                                                                                                                                       |

| E0000002 ? FDFE OK<br>OK<br>OK                                                                                                                                                                     |

## eP32\_xp2 Release

- All VHDL design files

- All eForth metacompiler files

- weForth system, an eForth implementation for Windows

- Documentation in ep32\_xp2.pdf

- Available at <u>http://www.offete.com</u> for \$25

### Take Home Messages

- We can break the yokes of Intel and Microsoft.

- We can explore the complete hardware/software space for the best solutions to our computing needs.

## Forth Organizations

- Forth Interest Group <u>http://www.forth.org</u>

A repository of public domain Forth systems and Forth documentation

- FORTH, Inc. <u>http://www.forth.com</u>

- SwiftForth, SwiftX for many microcontrollers

- MicroProcessor Engineering, Ltd. <u>http://www.mpeforth.com</u>

VFX Forth, Forth 7 Cross Compiler

# SVFIG -- Silicon Valley Forth Interest Group

- SVFIG meets every month at Stanford University to discuss the Forth language and its applications.

- For meeting announcements, please check:

http://www.forth.org/svfig/next.html http://www.meetup.com/SV-FIG/

# Thank You.